【88】SR-IOV

这篇文章已经写完半年,最近半年一直在适配各种国产CPU,一直没有时间整理。最近总算是把所有的国产CPU都适配完了。

0、前言

为了充分利用硬件资源,需要使用虚拟化技术。为了更准确地了解SR-IOV,我们来看一下SR-IOV产生的背景和研究历史。

1、传统的系统

传统的系统主要有下面的设备组成:

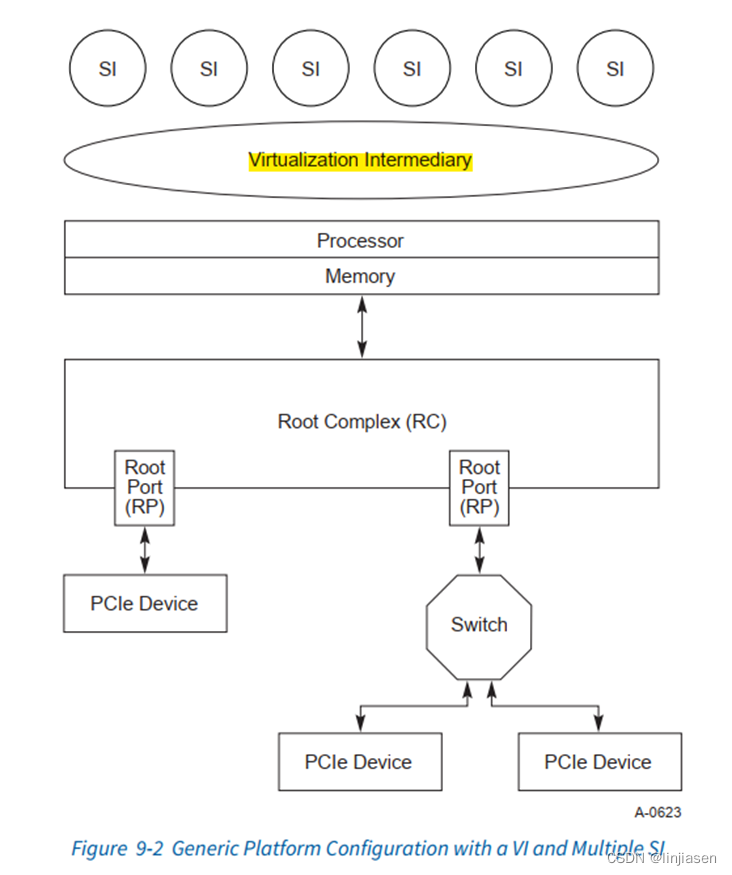

2、带有VI的系统

后面提高硬件资源利用效率,在不修改硬件的前提,在hardware和SI之间引入了VI(virtualiztion Intermediary),由软件来模拟硬件行为,在VI之上就是很多虚拟机。

VI独占下面的hardware资源,然后为每个SI抽象出硬件。由于IO操作需要通过VI处理,性能会受到显著影响,并且会增加系统资源开销。

为了减少系统资源开销,引入了SR-IOV技术。

3、SR-IOV系统

PF和VF都是被物理机的OS枚举的,VM访问VF BAR的时候使用的GVA (Guest Virtual Address), 这个IO操作会触发MMU把GVA翻译为GPA(Guest Physical Address), 这个GPA其实就是VM看到的VF的BAR地址空间,随后GPA会经过EPT(Expended Page Table)被翻译成HPA(Host Physical Address),这个HPA就是host上,或者说物理上的VF的BAR地址空间。

4、拥有SR-IOV的单PF设备

为了减少硬件资源,每个VF和PF share配置空间。

(1)VF使用和PF一样的配置header type。

(2)PF内的所有VF share VF BAR set,并且share SR-IOV寄存器的memory space enable(MSE)。

(3)InitialVFs和TotalVFs字段代表属于改PF的VF的最大数量。如果不支持VF migration,那么TotalVFs和InitialVFs应该一样。如果支持VF migration,那么TotalVFs代表可以被分配给该PF的数量,InitialVFs代表分配给该PF已经初始化的VF的数量。

每个PF和VF会分配唯一的Routing ID(bus、device、function)。

所有的PCIe和SR-IOV的配置访问只有VI或者SR-PCIM可以访问。

VF包含的non-shared的物理资源(例如work queue,data buffer)等是SI直接访问的,不需要通过VI或者SR-PCIM的干预。

5、SR-IOV初始化和资源分配

5.1配置VF的BAR

System Page Size字段定义了system映射VF的memory地址时的page size。如果system page size的 bit n是1,那么属于该PF的所有VF支持2^(n+12)次方page size对齐。

当system page size确定后,属于该PF的VF需要把BAR资源和system page size对齐。

写system page size时,VF enable bit应该为0。

iov.c

在PF枚举的初始化PCIe各种cap的时候会调用sriov_init初始化SR-IOV的cap。

pci_device_add->pci_init_capabilities->pci_iov_init->sriov_init

BARb VFv starting address = VF BARb + (v - 1) x (VF BARb aperture size)

对于同一个PF下的不同VF的同一个BARn,在memory空间上是连续的。因此,PF的SR-IOV寄存器只需要记录第一个VF的BAR的地址,其他VF的BAR的地址,需要通过上面公式计算。

我们找一个82599的网卡,enable 2个VF后看看PCIe资源

00:02.0 PCI bridge: Intel Corporation Xeon E5/Core i7 IIO PCI Express Root Port 2a (rev 07) (prog-if 00 [Normal decode])

Memory behind bridge: f7c00000-f7ffffff

Prefetchable memory behind bridge: 00000000f4000000-00000000f43fffff

Root Port下面预留了4M的地址。

03:00.0 Ethernet controller: Intel Corporation 82599ES 10-Gigabit SFI/SFP+ Network Connection (rev 01)

Capabilities: [160 v1] Single Root I/O Virtualization (SR-IOV)

IOVCap: Migration-, Interrupt Message Number: 000

IOVCtl: Enable+ Migration- Interrupt- MSE+ ARIHierarchy+

IOVSta: Migration-

Initial VFs: 64, Total VFs: 64, Number of VFs: 2, Function Dependency Link: 00

VF offset: 128, stride: 2, Device ID: 10ed

Supported Page Size: 00000553, System Page Size: 00000001

Region 0: Memory at 00000000f4000000 (64-bit, prefetchable)

Region 3: Memory at 00000000f4100000 (64-bit, prefetchable)

VF Migration: offset: 00000000, BIR: 0

PF0的Initial VFs: 64,表示归属PF0的已经初始化的VF个数是64

Total VFs: 64, 表示归属PF0的最大VF的个数是64

Number of VFs: 2,表示归属PF0的可用的VF的个数是2

VF offset: 128表示归属PF0的第1个VF的routing ID(bus:device.function)offset,用PF0的routing ID+这个字段就是第1个VF的routingID

stride: 2表示下1个VF的routing ID到前1个VF的routing ID的offset

struct pci_dev *dev是PF(3:0.0),int vf_id是VF的编号:

对于第2个VF(3:10.2)的bus=dev->bus->number + ((dev->dev_fun + dev->sriov->offset + dev->sriov->stride * vf_id) >>8) =3+((0+128+2*1)>>8)=3+0=3,第2个vf的bus=0x3

对于第2个VF(3:10.2)的devfun= (dev->dev_fun + dev->sriov->offset + dev->sriov->stride * vf_id) & 0xff = (0 + 128 + 2 * 1) & 0xff =0x82,第2个vf的device=0x10, function=0x2

Device ID: 10ed:表示SI看到的VF的deviceid

PF0的SR-IOV显示VF的BAR0的起始地址是f4000000,BAR3的起始地址是f4100000

从VF的BAR看VF0,VF1的BAR0和BAR3都是16K,64bit prefetchable的,也就是说PF0VF0- PF0VF63的BAR0占用64*16K=1M的大小,地址是f4000000到f4000000+(64*16K -1)= f400 0000+(0x10 0000-1)= f4000000~F40F FFFF

PF0VF0- PF0VF63的BAR3占用64*16K=1M的大小,PF0VF1的地址是f4100000到f4100000+(64*16K -1)= f4100000+(0x10 0000-1)= f4100000~F41F FFFF

03:00.1 Ethernet controller: Intel Corporation 82599ES 10-Gigabit SFI/SFP+ Network Connection (rev 01)

Capabilities: [160 v1] Single Root I/O Virtualization (SR-IOV)

IOVCtl: Enable- Migration- Interrupt- MSE- ARIHierarchy-

Initial VFs: 64, Total VFs: 64, Number of VFs: 0, Function Dependency Link: 01

Region 0: Memory at 00000000f4200000 (64-bit, prefetchable)

Region 3: Memory at 00000000f4300000 (64-bit, prefetchable)

PF1的VF虽然没有使能,但是地址还是预留的。

PF1VF0- PF0VF63的BAR0占用64*16K=1M的大小,地址是f4200000到f4200000+(64*16K -1)= f4000000+(0x10 0000-1)= f4200000~F42F FFFF

PF1VF0- PF0VF63的BAR3占用64*16K=1M的大小,地址是f4300000到f4300000+(64*16K -1)= f4300000+(0x10 0000-1)= f4300000~F43F FFFF

说明不管VF使能与否,RootPort都预留了对应的资源的

只有当SR-IOV的VF Enable和VF MSE都为1时,VF的memory空间才可以访问。修改System Page Size会影响VF BAR aperture。

6、SR-IOV Reset机制

6.1 SR-IOV Conventional Reset

Conventional reset将会导致PF和VF回到初始值。Conventional reset会导致PF的SR-IOV Control寄存器的VF Enable比特丢失,因此,Conventional reset后VF就不存在了。

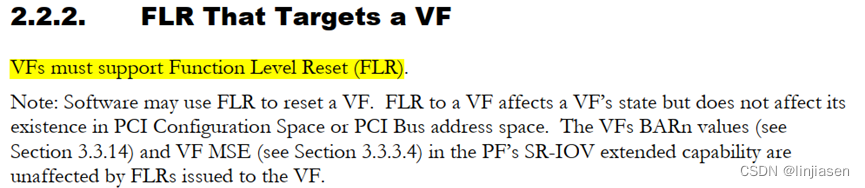

6.2 VF的FLR

VF的FLR只影响VF的state,不影响配置空间和PCI bus address space。PF的SR-IOV寄存器的VF的BAR和VF memory space enable不受影响,VF Resizable BAR capability 值也不受影响。

VF一定要支持FLR的,因为VM在probe VF的是会调用FLR(猜测这么做的原因是,VM不知道物理机是否曾经使用过VF,在自己用之前FLR一下,保证VF是初始状态)

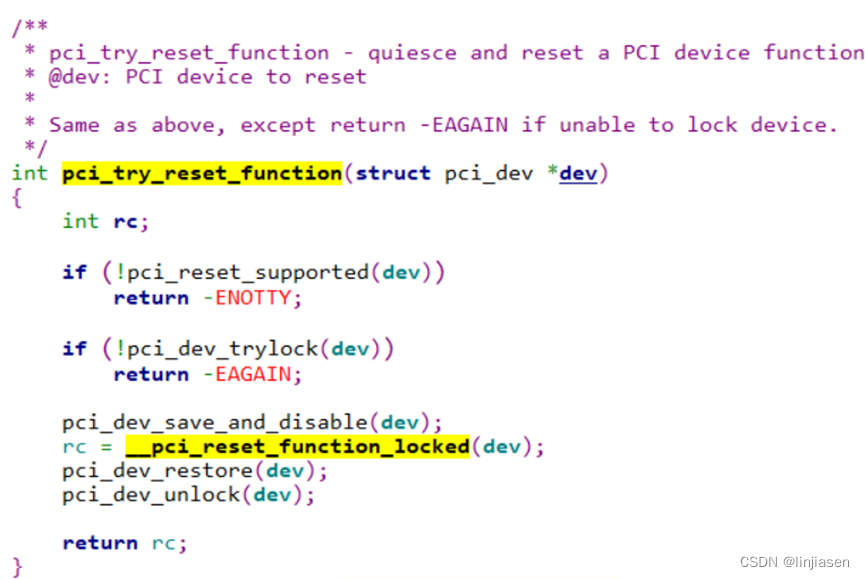

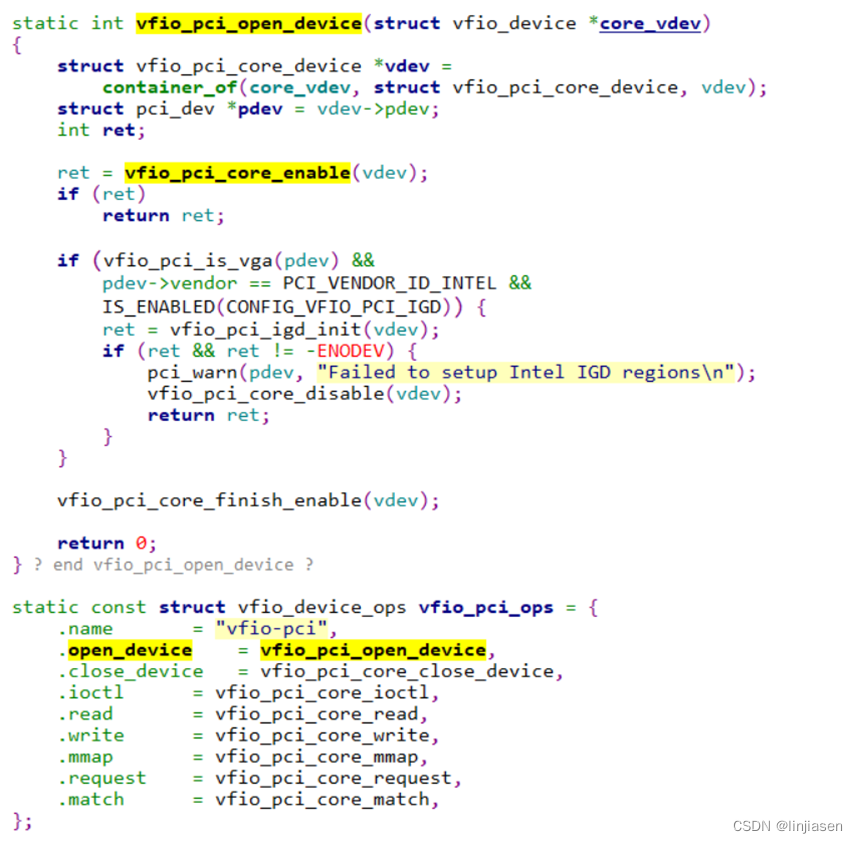

vfio_pci_open_device->vfio_pci_core_enable-> pci_try_reset_function-> __pci_reset_function_locked-> pci_reset_fn_methods[m].reset_fn-> pcie_reset_flr-> pcie_flr

cat /sys/bus/pci/devices/0000\:04\:00.0/reset_method 可以查看function支持哪些reset方式。

6.3 PF的FLR

PF的FLR会影响PF的state,并且SR-IOV寄存器的VF enable也会被影响。也就是说PF发生FLR,对应的VF 不存在了。

如果VF enable从1变成0,那么PF下面的所有VF都不存在了,VF不能发出PCIe transaction,也不能响应配置空间和memory空间的访问。VF也不会保存任何state(包括sticky的bit)

7、Linux对SR-IOV的支持

3. PCI Express I/O Virtualization Howto — The Linux Kernel documentation

有多种方式可以使能SR-IOV。

方式1:PF调用SR-IOV 的API(pci_enable_sriov / pci_disable_sriov)控制使能或者禁止。如果hardware有SR-IOV的cap,loading PF driver可以使能PF和归属于PF的所有VF。有些PF driver需要模块参数来设置enable VF的数量。

方式2:写sysfs文件系统sriov_numvfs 来使能或者禁止PF归属的VF(struct pci_driver.sriov_configure)

echo 'nr_virtfn' > /sys/bus/pci/devices/<DOMAIN:BUS:DEVICE.FUNCTION>/sriov_numvfs

7.1 枚举的PF时候初始化PF的SR-IOV capability

pci_device_add->pci_init_capabilities->pci_iov_init->sriov_init

- 读取PCI_SRIOV_CTRL,如果VF enable已经置1,则disable,并sleep 1秒

- 遍历dev->bus上的所有devcie,赋值给pdev,如果是PF,则跳转到found

- 读取PCI_SRIOV_TOTAL_VF,获取total的数量

- 设置page size

- 遍历SR-IOV的6个bar: PCI_SRIOV_NUM_BARS,赋值给iov的数据结构

- 读取PF SR-IOV的PCI_SRIOV_VF_DID,赋值给iov->vf_device

- 调用compute_max_vf_buses,计算pf需要消耗的bus数量

7.2 方式一:PF的probe函数使能SR-IOV(PF的probe调用pci_enable_sriov)

PF的probe->pci_enable_sriov->sriov_enable->sriov_add_vfs->pci_iov_add_virtfn

7.3 方式一:PF的remove函数disable SR-IOV

PF的remove->sriov_disable->sriov_del_vfs->pci_iov_remove_virtfn

7.4 方式二:使用sys文件系统使能SR-IOV

echo 'nr_virtfn' > /sys/bus/pci/devices/<DOMAIN:BUS:DEVICE.FUNCTION>/sriov_numvfs

sriov_numvfs_strore->struct pci_driver.sriov_configure-> pci_enable_sriov->sriov_enable-> sriov_add_vfs->pci_iov_add_virtfn

比如82599的网卡,一开始没有vf的,我们使能2个VF

echo 2 > /sys/bus/pci/devices/0000\:04\:00.0/sriov_numvfs

573

573

暂无认证

暂无认证

linjiasen: 你的说法是对的 ,只是如果按照spec上规定说register number 为 bit2~bit7,共6位,就得详细介绍怎么把256Byte的配置空间切割成64*4Byte,然后通过register number计算register offset,反而不如把IO address port最后8bit理解成registe offset好理解。我把这里重新写了,介绍了这么通过6bit的register number访问256byte的配置空间

,只是如果按照spec上规定说register number 为 bit2~bit7,共6位,就得详细介绍怎么把256Byte的配置空间切割成64*4Byte,然后通过register number计算register offset,反而不如把IO address port最后8bit理解成registe offset好理解。我把这里重新写了,介绍了这么通过6bit的register number访问256byte的配置空间

Rob月初: 写得不错,不过纠正一点,CAM方式时,register number 为 bit2~bit7,共6位,并不是文中的8bits噢,能访问256bytes也是因为2的6次幂(也就是64)* 32bit CONFIG_DATA = 256byte。

linjiasen: pci-express-technology-30_compress.pdf已经发送,附件超大,请及时查收

沙舍: 1971530550@qq.com 楼主麻烦也发一下 谢谢哦

linjiasen: 是的,需要公司在PCI SIG注册后才可以下载,你要是没有给我个联系方式,我发给你